CrashTest

A Fast High-Fidelity FPGA-Based Resiliency Analysis Framework

About

CrashTest is a fast, high-fidelity, flexible resiliency analysis system. Starting from a hardware description model of the design under analysis, CrashTest is capable of orchestrating and performing a comprehensive design resiliency analysis by examining how the design reacts to faults while running software applications.

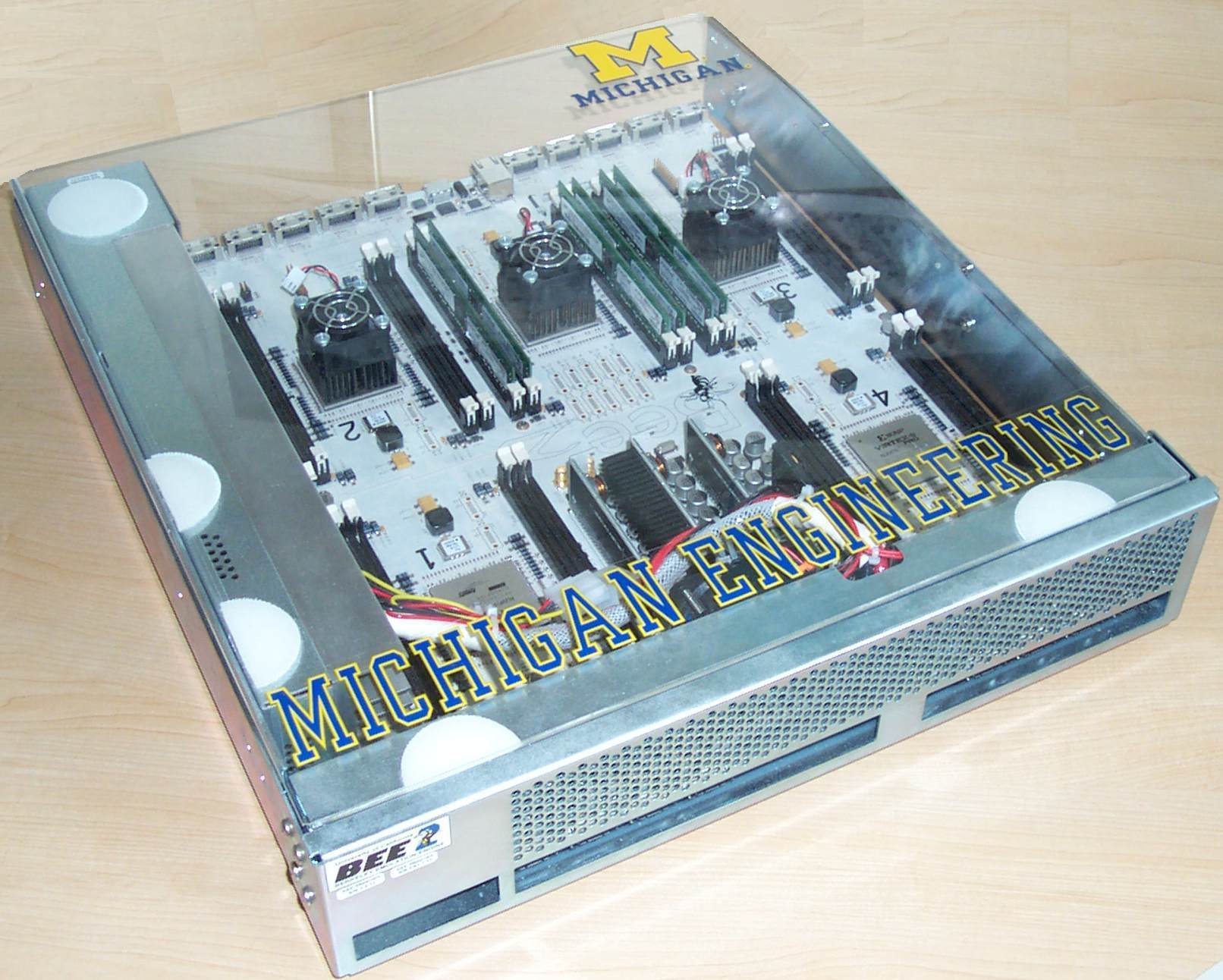

CrashTest provides a high-fidelity analysis report obtained by performing a fault injection campaign at the gate-level netlist of the design. The fault injection and analysis process is significantly accelerated by the use of an FPGA hardware emulation platform.

CrashTest is available out of the box for Leon3 and OpenSPARC T1 on the Xilinx University Program XUPV5-LX110T Development System

The current version of Crashtest has been tested on designs synthesized with the Synopsys GTECH library and supports the following fault models: bridge, path-delay, stuck-at, stuck-open, and transient.

CrashTest has been developed at the University of Michigan, Ann Arbor and it is publicly available under GPL license v2.0.

Documentation:

Basic CrashTest:

The basic version of CrashTest for Leon3 and OpenSPARC T1 consists of the following:

- Bitstreams for XUPV5-LX110T board - OpenSPARC T1 Leon3

- Fault-free netlists (generated with Synopsys DC) - OpenSPARC T1 Leon3

- Fault-ready netlists - OpenSPARC T1 Leon3

- Firmware for fault injection manager - OpenSPARC T1 Leon3

Customize CrashTest:

CrashTest can be customized to work with any design and technology library. Scripts to inject faults and projects to adapt Crashtest to any design and FPGA device are below:

- Synthesis script - OpenSPARC T1 Leon3

- Fault injection script - Script

- Synopsys Synplify projects for XUPV5-LX110T board - OpenSPARC T1 Leon3

- Xilinx EDK projects for XUPV5-LX110T board - OpenSPARC T1 Leon3

Project Members

- Andrea Pellegrini

- Valeria Bertacco

- Todd Austin

- Kypros Constantinides

- Junhao Jiang

- Shobana Sudhakar

- Dan Zhang

Publications

- "CrashTest: A fast High-Fidelity FPGA-based Resiliency Analysis Framework"

Andrea Pellegrini, Kypros Constantinides, Dan Zhang, Shobana Sudhakar, Valeria Bertacco and Todd Austin

IEEE International Conference on Computer Design (ICCD), Lake Tahoe, CA, October 2008 - "Fault-Based Attack of RSA Authentication"

Andrea Pellegrini, Valeria Bertacco and Todd Austin

Design Automation and Test in Europe (DATE), Dresden, Germany, March 2010